|                   | Name Description Usage                                                       |

|-------------------|------------------------------------------------------------------------------|

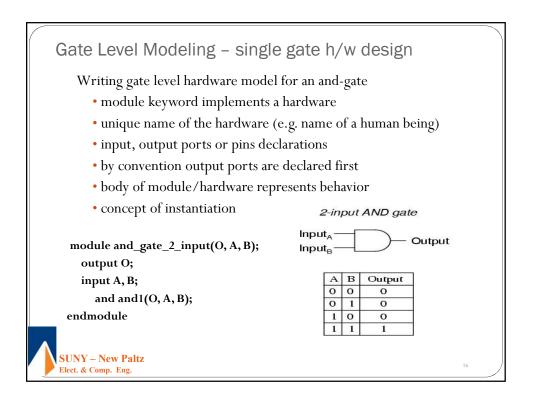

| Verilog language  | and $f = (a \cdot b \cdots)$ and $(f, a, b, \ldots)$                         |

| provides basic    | nand $f = \overline{(a \cdot b \cdots)}$ nand( $f, a, b, \dots$ )            |

| gates as built-in | or $f = (a + b +)$ or $(f, a, b,)$                                           |

| primitives        | nor $f = \overline{(a+b+\cdots)}$ nor $(f, a, b, \ldots)$                    |

|                   | <b>x</b> or $f = (a \oplus b \oplus \cdots)$ <b>x</b> or (f, a, b,)          |

| as shown,         | <b>x</b> nor $f = (a \odot b \odot \cdots)$ <b>x</b> nor $(f, a, b, \ldots)$ |

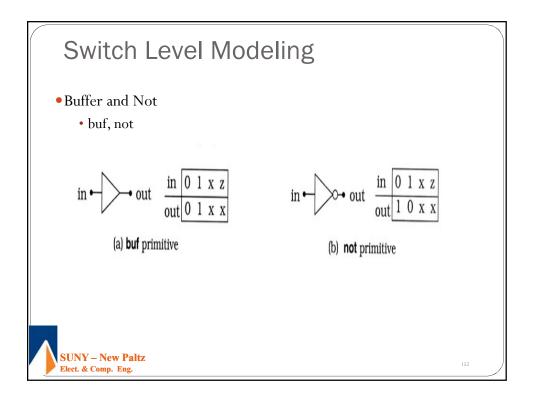

| aka white box     | not $f = a$ not $(f, a)$                                                     |

|                   | buf $f = a$ buf(f, a)                                                        |

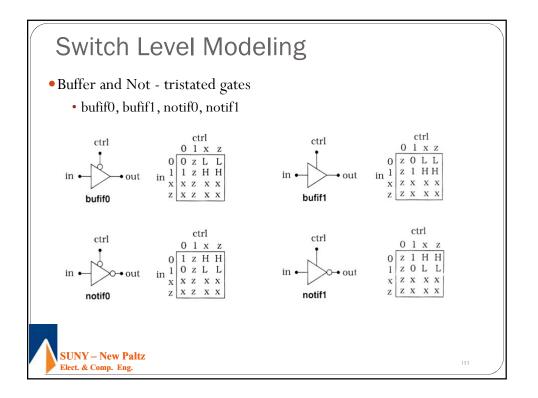

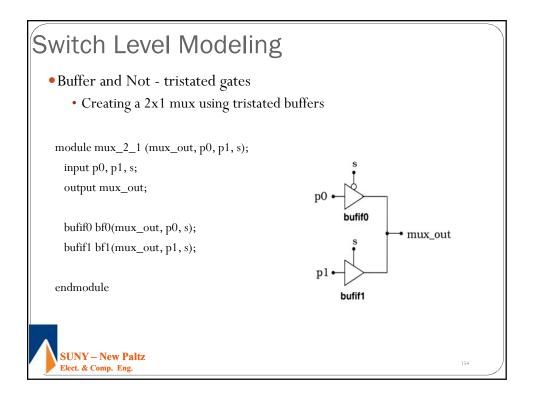

|                   | notif0 $f = (!e?\overline{a}:'bz)$ notif0(f, a, e)                           |

|                   | notifl $f = (e?\overline{a}: bz)$ notifl(f, a, e)                            |

|                   | bufif0 $f = (!e?a:'bz)$ bufif0(f,a,e)                                        |

|                   | $\texttt{bufif1} f = (e?a: bz) \qquad \texttt{bufif1}(f, a, e)$              |

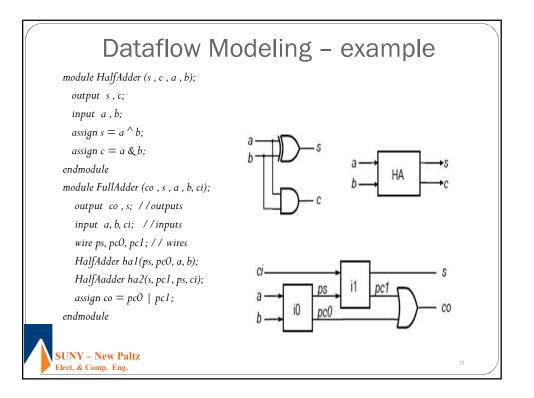

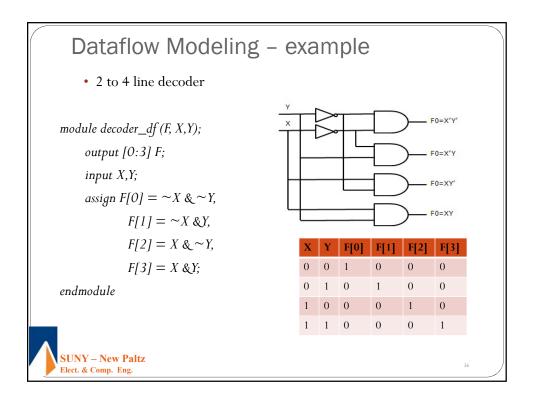

| ck box wh<br>ters | ere bitwise op                               | erators are used for data flow between                                                 |

|-------------------|----------------------------------------------|----------------------------------------------------------------------------------------|

|                   | <b>ign</b> is used for                       | dataflow modeling                                                                      |

|                   | e                                            | e                                                                                      |

| age of assig      | gnment operat                                | or = results in continuous assignment                                                  |

| 8                 |                                              |                                                                                        |

| 0                 | etors                                        |                                                                                        |

| twise oper        | ators                                        |                                                                                        |

| twise oper        |                                              | Examples                                                                               |

| 0                 | ators Operation                              | <b>Examples</b><br>a = 3'b101, b = 3'b110, c = 3'b01x                                  |

| twise oper        |                                              |                                                                                        |

| twise oper        | Operation                                    | a = 3'b101, b = 3'b110, c = 3'b01x                                                     |

| operator          | Operation<br>invert each bit                 | a = 3'b101, b = 3'b110, c = 3'b01x<br>~a is 3'b010                                     |

| operator          | Operation<br>invert each bit<br>and each bit | a = 3'b101, b = 3'b110, c = 3'b01x<br>~a is 3'b010<br>a & b is 3'b100, b & c is 3'b010 |

| always<br>and<br>assign<br>attribute<br>begin<br>buf<br>bufifD<br>bufifD<br>case<br>casex<br>casez<br>casex<br>casez<br>cmos<br>deassign<br>default<br>defparam<br>disable<br>edge<br>else<br>end<br>end<br>endattribute<br>endcase<br>endfunction | endmodule<br>endprimitive<br>endspecify<br>endtable<br>endtask<br>event<br>for<br>force<br>forker<br>function<br>highz0<br>highz1<br>if<br>ifnone<br>initial<br>inout<br>input<br>integer<br>join<br>medium<br>module | large<br>macromodule<br>nand<br>negedge<br>nmos<br>nor<br>not<br>notifO<br>notif1<br>or<br>output<br>parameter<br>pmos<br>posedge<br>primitive<br>pull0<br>pull1<br>pulldown<br>pullup<br>rcmos<br>real<br>realtime | reg<br>release<br>repeat<br>rmmos<br>rpmos<br>rtran<br>rtranifD<br>rtranif1<br>scalared<br>signed<br>small<br>specfy<br>specparam<br>strength<br>strong0<br>strong1<br>supply0<br>supply1<br>table<br>task<br>time<br>tran | tranifD<br>tranif1<br>tri<br>triD<br>tri1<br>triand<br>trior<br>trireg<br>unsigned<br>vectored<br>wait<br>wand<br>weak0<br>weak1<br>while<br>wire<br>wor<br>xnor<br>xor |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Insight into Verilo                     | og language – bnf, syntax, semantics – exampl | e \ |

|-----------------------------------------|-----------------------------------------------|-----|

| module definition                       | 1                                             |     |

| module m                                | odule name [(port name{, port name})];        |     |

|                                         | [parameter declaration]                       |     |

|                                         | [input declaration]                           |     |

|                                         | [output declaration]                          |     |

|                                         | [inout declaration]                           |     |

|                                         | [net declaration]                             |     |

|                                         | [reg declaration]                             |     |

|                                         | [time declaration]                            |     |

|                                         | [integer declaration]                         |     |

|                                         | [real declaration]                            |     |

|                                         | [event declaration]                           |     |

|                                         | [gate declaration]                            |     |

|                                         | [UDP instantiation]                           |     |

|                                         | [function or task]                            |     |

|                                         | [continuous assign]                           |     |

|                                         | [specify block]                               |     |

|                                         | [initial statement]                           |     |

|                                         | [always statement]                            |     |

|                                         | [module instantiation]                        |     |

| endmodul                                | e                                             |     |

| SUNY – New Paltz<br>Elect, & Comp. Eng. | 40                                            | ,   |

| F ERCU & Comp. Eng.                     |                                               |     |

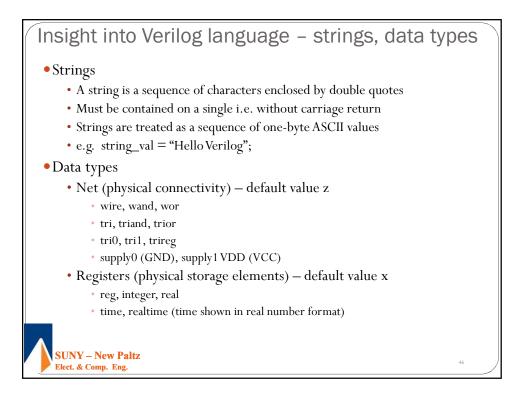

Insight into Verilog language – data types - net

- "wor" performs "or" operation on multiple driver logic

- "wand" performs "and" operation on multiple driver logic

- "trior" and "triand" perform the same function as "wor" and "wand", but model outputs with resistive loads

| net type<br>wire<br>tri    | modeling usage<br>Net with single driver<br>Net with multiple driver |

|----------------------------|----------------------------------------------------------------------|

| wand, triand<br>wor, trior | Model wired logic function at gate level                             |

| tri0, tri1                 | Pulls up or down the net at gate level                               |

| trireg                     | Stores the value at previous level (gate)                            |

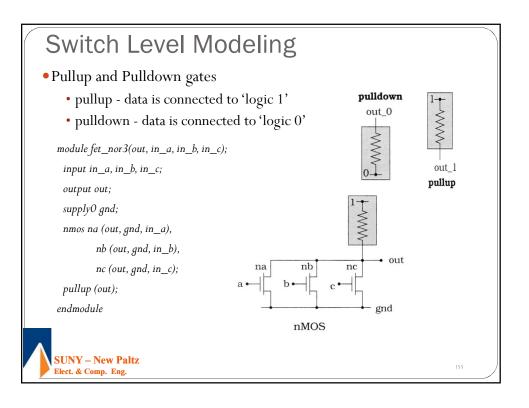

| supply0<br>supply1         | Constant logic 0 at switch level<br>Constant logic 1 at switch level |

| Paltz                      |                                                                      |

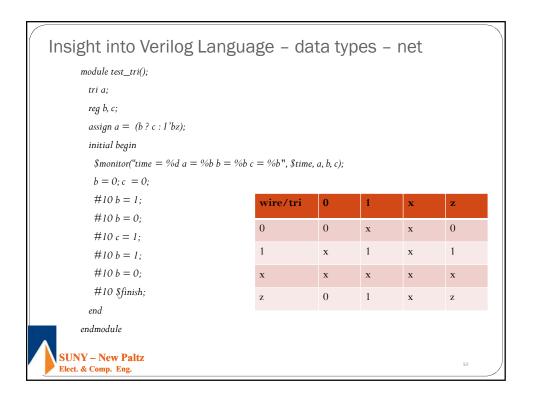

| Insight into Ve                         | rilog Lar        | nguag          | e – d         | ata t | ypes - | - net |  |

|-----------------------------------------|------------------|----------------|---------------|-------|--------|-------|--|

| <pre>module test_wor(); wor a;</pre>    |                  |                |               |       |        |       |  |

| reg b, c;                               |                  |                |               |       |        |       |  |

| assign $a = b;$                         |                  |                |               |       |        |       |  |

| assign a = c;<br>initial begin          |                  |                |               |       |        |       |  |

| \$monitor("time = %                     | bd a = %b b = %b | c = %b", \$tin | ne, a, b, c); |       |        |       |  |

| #10 b = 0;                              |                  |                |               |       |        |       |  |

| #10 c = 0;                              | wor/trior        | 0              | 1             | x     | z      |       |  |

| #10 b = 1;<br>#10 b = 0;                |                  |                |               |       |        |       |  |

| #10 c = 1;                              | 0                | 0              | 1             | x     | 0      |       |  |

| #10 b = 1;                              | 1                | 1              | 1             | 1     | 1      |       |  |

| #10 b = 0;                              | х                | x              | 1             | x     | x      |       |  |

| #10 \$finish;<br>end                    | z                | 0              | 1             | x     | z      |       |  |

| endmodule                               |                  |                |               |       |        |       |  |

| SUNY – New Paltz<br>Elect. & Comp. Eng. |                  |                |               |       |        | 48    |  |

| Insight into Ver                        | ilog Lang                       | uage -               | data | types - | - net |

|-----------------------------------------|---------------------------------|----------------------|------|---------|-------|

| <pre>module test_wand();</pre>          |                                 |                      |      |         |       |

| wand a;                                 |                                 |                      |      |         |       |

| reg b, c;                               |                                 |                      |      |         |       |

| assign $a = b;$                         |                                 |                      |      |         |       |

| assign $a = c;$                         |                                 |                      |      |         |       |

| initial begin                           |                                 |                      |      |         |       |

| \$monitor("time = %d a =                | $= \% b \ b = \% b \ c = \% b'$ | ', \$time, a, b, c); |      |         |       |

| #10 b = 0;                              |                                 |                      |      |         |       |

| #10 c = 0;                              |                                 |                      |      |         |       |

| #10 b = 1;                              | wand/triand                     | 0                    | 1    | х       | z     |

| #10 b = 0;                              |                                 |                      |      |         |       |

| #10 c = 1;                              | 0                               | 0                    | 0    | 0       | 0     |

| #10 b = 1;                              | 1                               | 0                    | 1    | x       | 1     |

| #10 b = 0;                              | x                               | 0                    | x    | x       | x     |

| #10 \$finish;                           | x                               |                      |      | х       | x     |

| end                                     | z                               | 0                    | 1    | х       | z     |

| endmodule                               |                                 |                      |      |         |       |

| SUNY – New Paltz<br>Elect. & Comp. Eng. |                                 |                      |      |         | 49    |

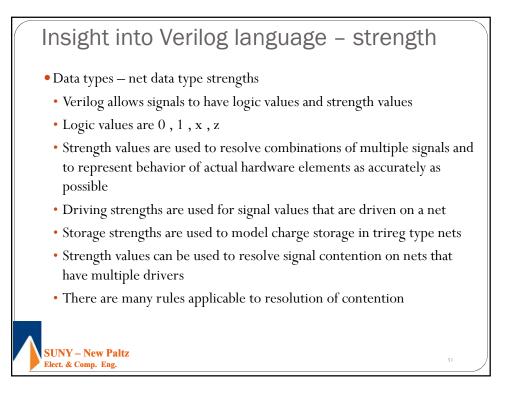

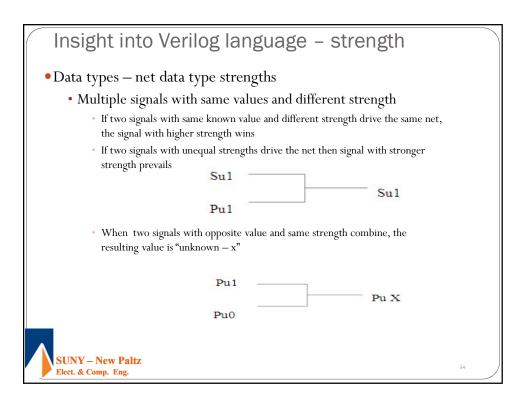

| Data types                       | – net data            | ilog langu<br>type strength<br>ntention , value | S                 | _              |

|----------------------------------|-----------------------|-------------------------------------------------|-------------------|----------------|

| strengtl<br>Strength<br>Level    | h<br>Strength<br>Name | Abbreviation                                    | Strength<br>Level | Strength       |

|                                  |                       |                                                 |                   | Туре           |

| 7                                | supply1               | su1                                             | strongest1        | driving        |

| 6                                | strong1               | st1                                             | strongest1        | driving        |

| 5                                | pull1                 | pu1                                             | strongest1        | driving        |

| 4                                | large1                | la1                                             | strongest1        | storage        |

| 3                                | weak1                 | we1                                             | strongest1        | driving        |

| 2                                | medium1               | me1                                             | strongest1        | storage        |

| 1                                | small1                | sm1                                             | strongest1        | storage        |

| 0                                | highz1                | hiz1                                            | weakest1          | High impedance |

| SUNY – New I<br>Ilect. & Comp. E | Paltz                 |                                                 |                   | 52             |

| •Data t | ypes – ne              | et data typ      | g langua<br>be strengths<br>ntion , value is |                   | rength<br>sing logic streng | th |

|---------|------------------------|------------------|----------------------------------------------|-------------------|-----------------------------|----|

|         | Strengt<br>h<br>Level  | Strength<br>Name | Abbreviation                                 | Strength<br>Level | Strength<br>Type            |    |

|         | 7                      | supply0          | su0                                          | strongest0        | driving                     |    |

|         | 6                      | strong0          | st0                                          | strongest0        | driving                     |    |

|         | 5                      | pull0            | pu0                                          | strongest0        | driving                     |    |

|         | 4                      | large0           | la0                                          | strongest0        | storage                     |    |

|         | 3                      | weak0            | we0                                          | strongest0        | driving                     |    |

|         | 2                      | medium0          | me0                                          | strongest0        | storage                     |    |

|         | 1                      | small0           | sm0                                          | strongest0        | storage                     |    |

|         | 0                      | highz0           | hiz0                                         | weakest0          | High impedance              |    |

|         | New Paltz<br>omp. Eng. |                  |                                              |                   |                             | 53 |

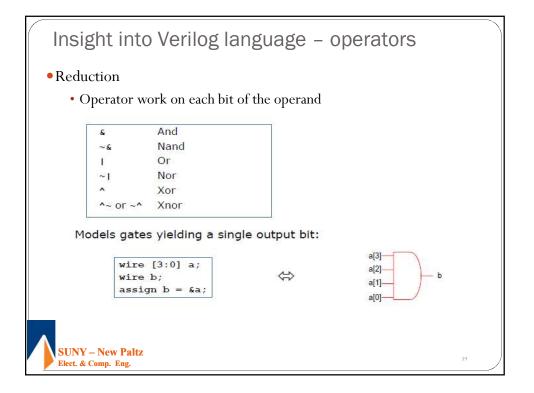

|             | 11.4               | 1                                  |

|-------------|--------------------|------------------------------------|

|             | on each bit of o   | 1                                  |

| • Result is | in the size of the | e largest operand                  |

| • Left exte | nded if the sizes  | are different                      |

| Operator    | Operation          | Examples                           |

|             |                    | a = 3'b101, b = 3'b110, c = 3'b01x |

| ~           | invert each bit    | ~a is 3'b010                       |

| &           | and each bit       | a & b is 3′b100, b & c is 3′b010   |

| I           | or each bit        | a   b is 3'b111                    |

| ^           | xor each bit       | a ^ b is 3'b011                    |

|             | xnor each bit      | a ^~ b = 3'b100                    |

| Logical<br>• Can eval | uate to 1, 0, x v | values                                     |

|-----------------------|-------------------|--------------------------------------------|

|                       |                   | e (1) or false (0)                         |

| Operator              | Operation         | <b>Examples</b><br>a = 4, b = 0, c = 2'b0x |

| <b>3</b> 3            | logical and       | a & b = 0, a & c = x, b & c = 0            |

| П                     | logical or        | a    b = 1, a    c = 1, b    c = x         |

| !                     | arithmetic not    | !a = 0, !b = 1, !c = x                     |

| nift           |                                  |                                                                |

|----------------|----------------------------------|----------------------------------------------------------------|

| • Shifts the   | bit of a vector left or rig      | ght                                                            |

| • Shifted bit  | are lost                         |                                                                |

| • Arithmeti    | c shift right fills the shif     | ted bits with sign bit                                         |

| • All others   | fill the shifted bits by z       | 2ro                                                            |

| in others      |                                  |                                                                |

| Operator       | Operation                        | Examples<br>ain = 4'b1010, bin = 4'b10X0                       |

|                | ,                                | Examples                                                       |

| Operator       | Operation                        | Examples<br>ain = 4'b1010, bin = 4'b10X0                       |

| Operator<br>>> | Operation<br>logical shift right | Examples<br>ain = 4'b1010, bin = 4'b10X0<br>bin >> 1 = 4'b010X |

| elational   |                             |                                |

|-------------|-----------------------------|--------------------------------|

| • Evaluates | to 1, 0, x                  |                                |

| • Result in | x if any operan             | d bit is z or x                |

| Operator    | Operation                   | Examples                       |

| operator    | operation                   | a = 4, b = 0, c = 2'b0x        |

| >           | greater than                | (a > b) = 1, (b > a) = 0       |

| >=          | greater than<br>or equal to | $(a \ge 4) = 1, (b \ge c) = x$ |

| <           | less than                   | (a > b) = 0, (b > a) = 1       |

| <=          | less than<br>or equal to    | (b <= a) = 1, (b <= 0) = 1     |

| Juality      |                    |                                                                  |

|--------------|--------------------|------------------------------------------------------------------|

| • assign Wri | iteMe = (wr =      | == 1) &&                                                         |

|              | ((a                | >= 16'h7000) && (a < 16'h8000));                                 |

| 0            | 0                  | Desult                                                           |

| Operator     | Operation          | Result                                                           |

| ==           | logical            | 1 if operands are equal,<br>0 if operands are not equal,         |

|              | equality           | x if x or z in either operand                                    |

| !=           | logical            | 1 if operands are not equal,                                     |

|              | inequality         | 0 if operands are equal,<br>x if x or z in either operand        |

| ===          | case<br>equality   | 1 if operands are equal, <i>including x an z</i> , else 0        |

| !==          | case<br>inequality | 1 if operands are not equal, <i>including</i> )<br>and z, else 0 |

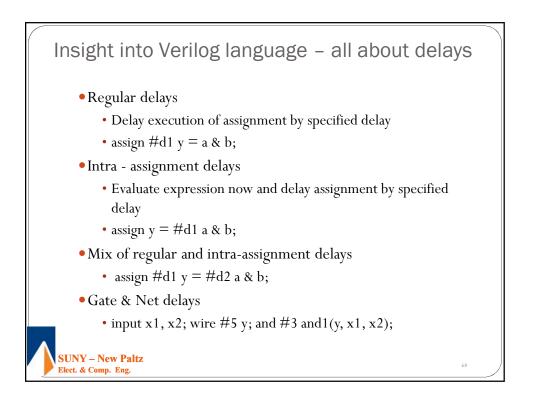

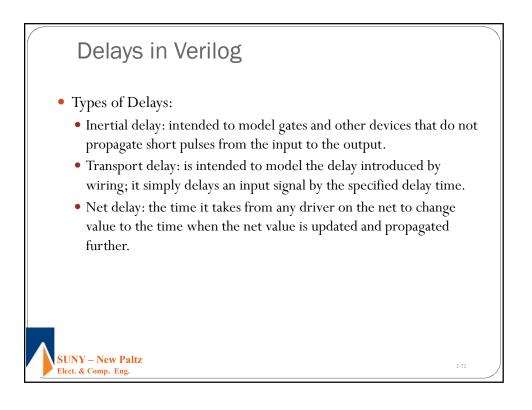

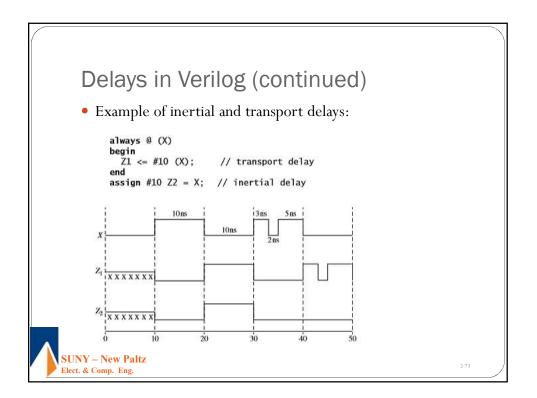

Insight into Verilog language - delay example Insight into Verilog language – delay example module delaytb; reg a = 1, b = 0, c = 0, d = 0; initial begin // stimulus block #15 a = 0;#20 \$finish; end initial begin /\* Regular delay control: evaluate expression at time = 10 \*/ #10 c = a | b;/\* Intra-assignment delay control: evaluate expression now then wait 10 time units to assign value to d \*/ d = #10 a | b;end endmodule SUNY – New Paltz Elect. & Comp. Eng.

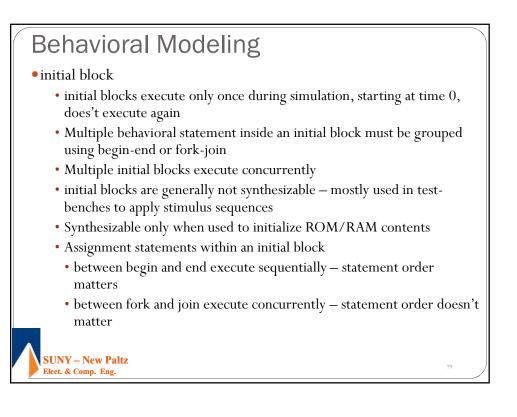

| • initial block example                                             |      |                     |

|---------------------------------------------------------------------|------|---------------------|

| module system;<br>reg a, b, c, d;                                   |      |                     |

| <pre>// single statement initial</pre>                              | Time | Statement Executed  |

| <pre>/* multiple statements     need to be grouped */ initial</pre> | 0    | a = 1'b0; b = 1'b1; |

| begin<br>b = 1'b1;<br>#5 c = 1'b0;                                  | 5    | c = 1′b0;           |

| #10 d = 1'b0;<br>end                                                | 15   | d = 1'b0;           |

| initial<br>#20 \$finish;                                            | 20   | \$finish;           |

| endmodule                                                           |      |                     |

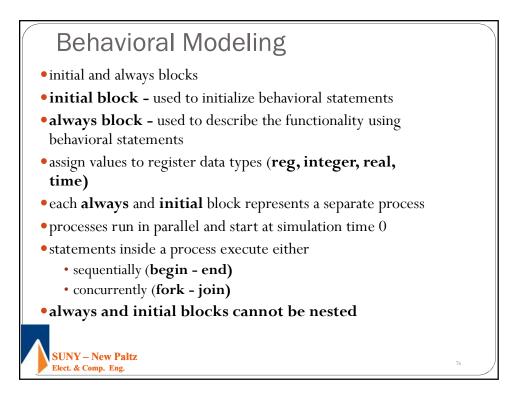

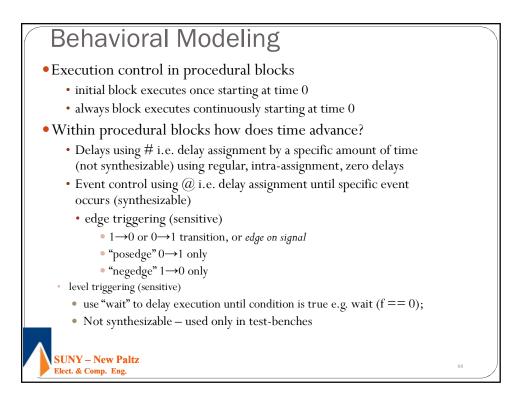

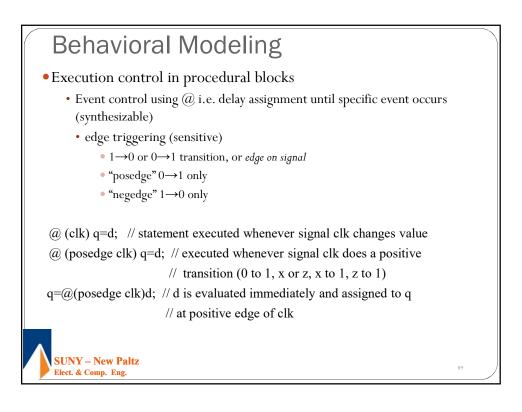

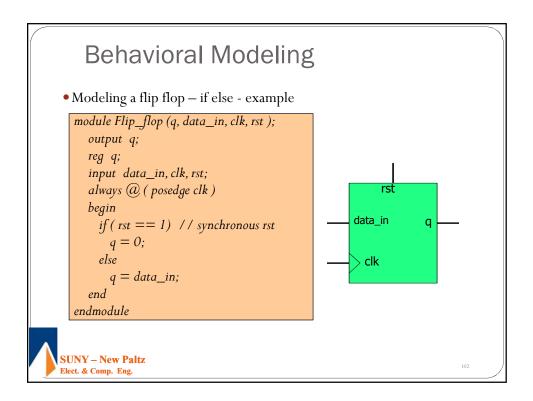

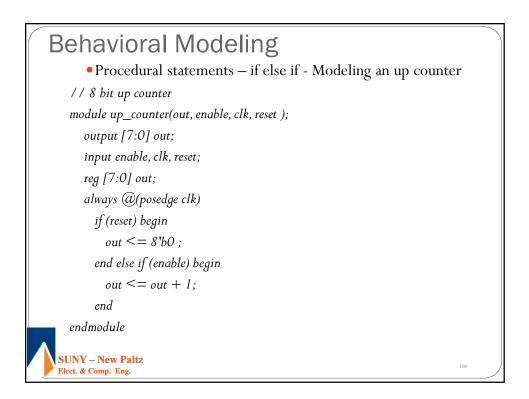

**Behavioral Modeling**  Execution control in procedural blocks • Event control using @ - sequential logic forms // q = d executed whenever clock changes always @(clock) q = d; // q = d executed on rising edge (0->1) of clk always @(posedge clk) q = d; // q = d executed on falling edge (1->0) of clk always @(negedge clk) q = d; // flip-flop with asynchronous reset always @(posedge clock, negedge reset n) if (!reset\_n) q = 0;else q = d;SUNY – New Paltz Elect. & Comp. Eng.

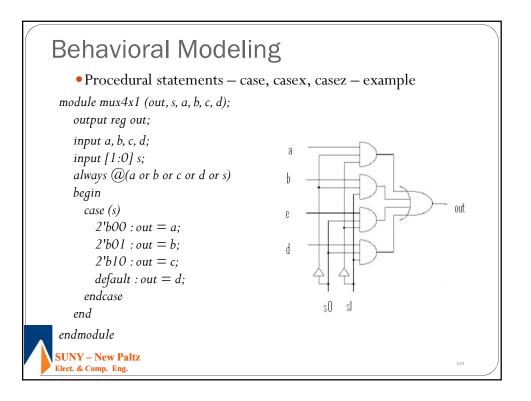

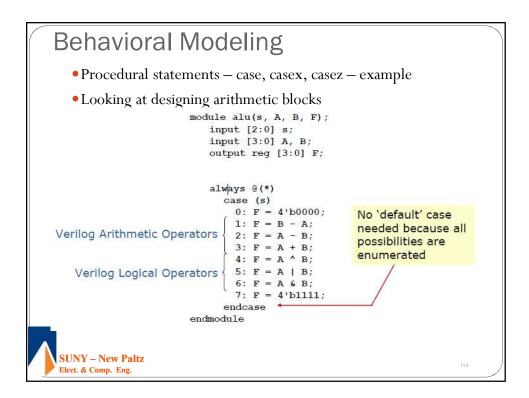

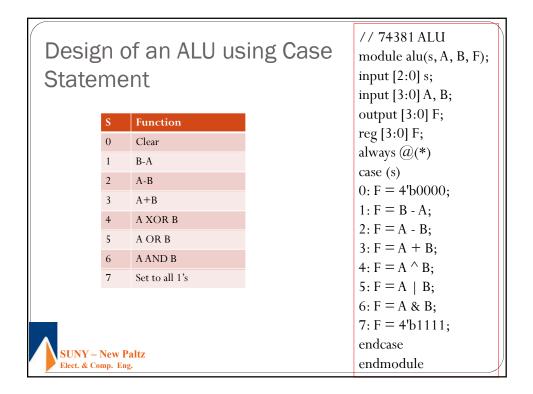

|   | g at designing a | – case, casex, casez<br>rithmetic blocks – I | 1                 | 74381 |

|---|------------------|----------------------------------------------|-------------------|-------|

|   | Operation        | Inputs (S2 S1 S0)                            | Functional output |       |

|   | CLEAR            | 000                                          | 0000              |       |

|   | B - A            | 001                                          | B - A             |       |

|   | A - B            | 010                                          | A - B             |       |

|   | ADD              | 011                                          | A + B             |       |

|   | XOR              | 100                                          | A xor B           |       |

|   | OR               | 101                                          | A or B            |       |

|   | AND              | 110                                          | A and B           |       |

|   | PRESET           | 111                                          | 1111              |       |

| _ |                  |                                              |                   |       |

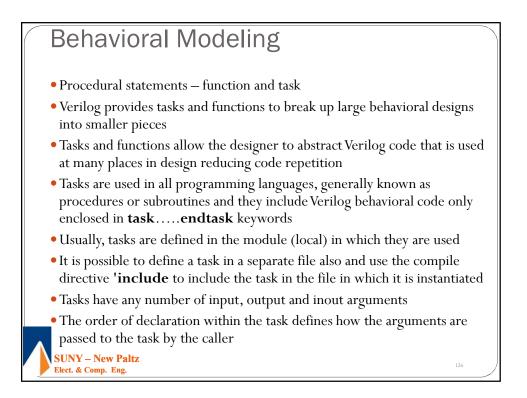

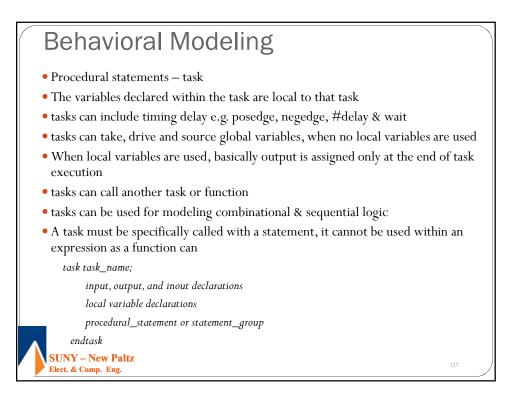

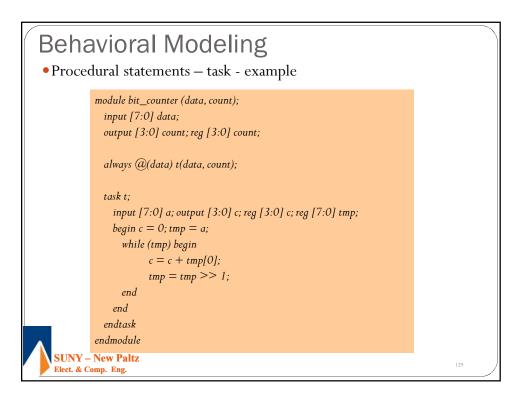

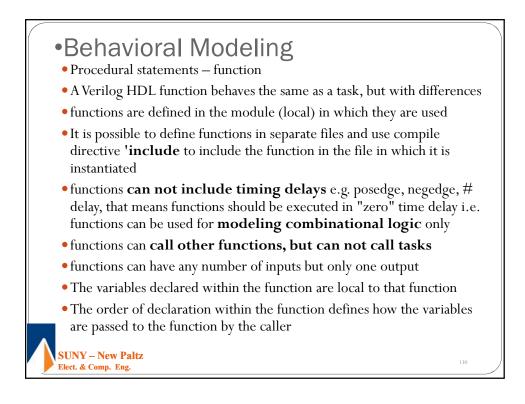

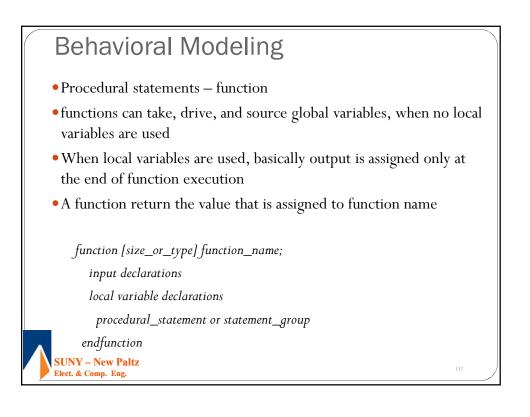

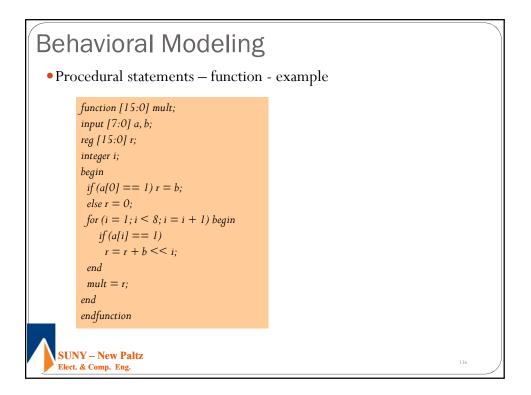

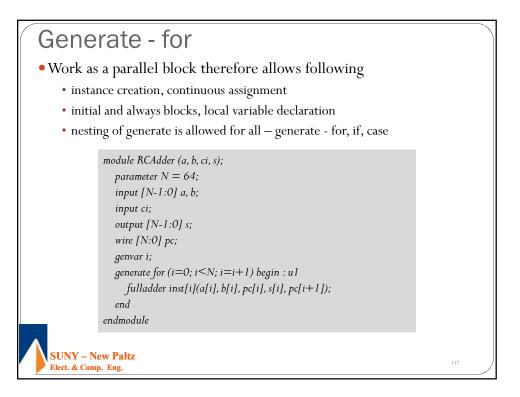

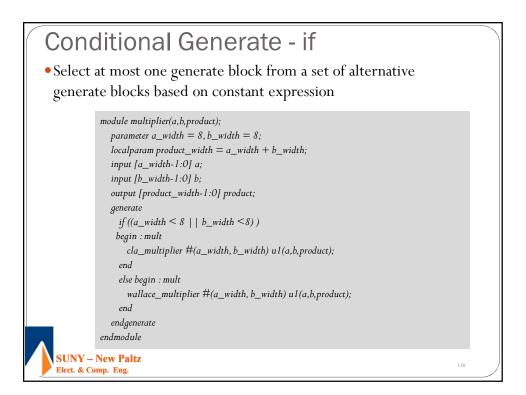

| Behavioral Modeling <ul> <li>Procedural statements – task - example</li> </ul>                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                          |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <pre>task convert;<br/>input [7:0] temp_in;<br/>output [7:0] temp_out;<br/>begin<br/>temp_out = (9/5)*(temp_in + 32);<br/>end<br/>endtask<br/>// task with globals<br/>reg [7:0] temp_out;<br/>teg [7:0] temp_in;<br/>task convert;<br/>begin<br/>temp_out = (9/5)*(temp_in + 32);<br/>end<br/>endtask</pre> | <pre>module callingtask (temp_a, temp_b, temp_c, temp_d);<br/>input [7:0] temp_a, temp_c;<br/>output [7:0] temp_b, temp_d;<br/>reg [7:0] temp_b, temp_d;<br/>`include "mytask.v"<br/>always @ (temp_a) begin<br/>convert (temp_a, temp_b);<br/>end<br/>always @ (temp_c) begin<br/>convert (temp_c, temp_d);<br/>end<br/>endmodule</pre> |  |  |

| SUNY – New Paltz<br>Elect. & Comp. Eng.                                                                                                                                                                                                                                                                      | 128                                                                                                                                                                                                                                                                                                                                      |  |  |

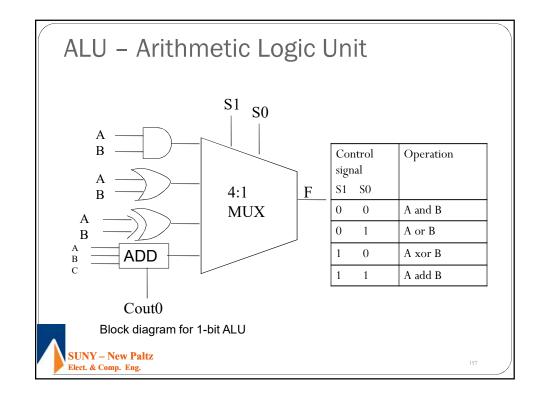

| <ul> <li>ALU – Arithmetic Logic Unit</li> <li>// 1-bit alu<br/>module mux(f, s0, s1, w, x, y, z);<br/>output f;<br/>input s0, s1, w, x, y, z;<br/>assign f = s1 ? (s0 ? x : y) : (s0 ? w :<br/>z);<br/>endmodule</li> <li>module fulladder(z, c0, a, b, c);<br/>output z, c0;<br/>input a,b,c;<br/>assign z = a ^ b ^ c;<br/>assign c0 = (a&amp;b)   (b&amp;c)   (c&amp;a);<br/>endmodule</li> </ul> | <pre>// 1-bit alu module alu(F, CO, SO, S1, A, B, C); output F, CO; input SO, S1, A, B, C; wire w, x, y, z; and a1(w, A, B); or o1(x, A, B); xor x1(y, A, B); fulladder f1(z, CO, A, B, C); mux m1(F, SO, S1, w, x, y, z); endmodule</pre> |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

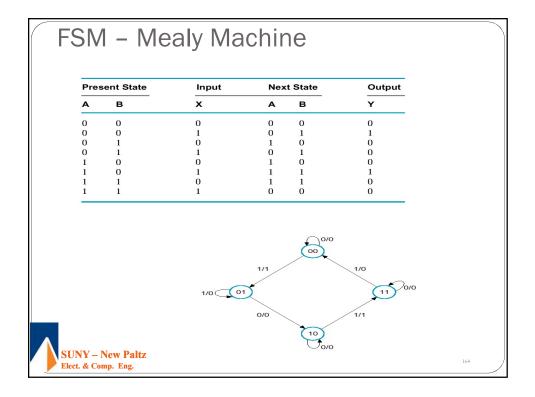

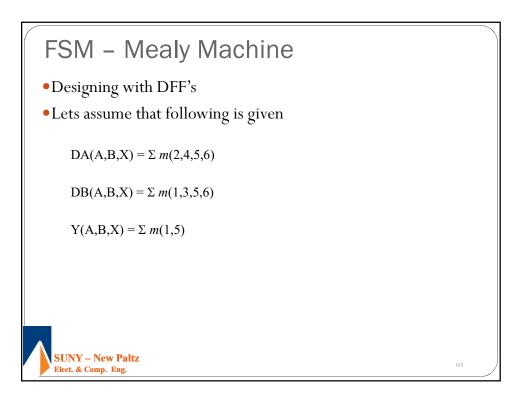

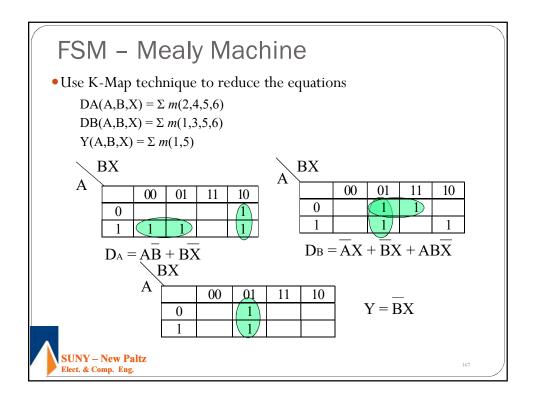

| D<br>D                   | A(A,B,X) = | y Machir<br>= Σ m(2,4,5,6<br>= Σ m(1,3,5,6)<br>Σ m(1,5) | )          |   |        |

|--------------------------|------------|---------------------------------------------------------|------------|---|--------|

|                          | sent State | Input                                                   | Next State |   | Output |

| Α                        | В          | x                                                       | Α          | в | Y      |

| 0                        | 0          | 0                                                       | 0          | 0 | 0      |

| 0                        | 0          | 1                                                       | 0          | 1 | 1      |

| 0                        | 1          | 0                                                       | 1          | 0 | 0      |

| 0                        | 1          | 1                                                       | 0          | 1 | 0      |

| 1                        | 0          | 0                                                       | 1          | 0 | 0      |

| 1                        | 0          | 1                                                       | 1          | 1 | 1      |

| 1                        | 1          | 0                                                       | 1          | 1 | 0      |

| 1                        | 1          | 1                                                       | 0          | 0 | 0      |

| SUNY – N<br>Elect. & Com |            |                                                         |            |   | 166    |

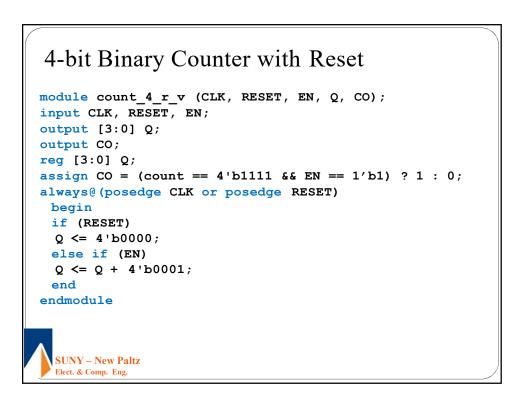

# 4-bit Shift Register with Reset module srg\_4\_r\_v (CLK, RESET, SI, Q,SO); input CLK, RESET, SI; output [3:0] Q; output SO; **reg** [3:0] Q; assign SO = Q[3]; always@(posedge CLK or posedge RESET) begin if (RESET) Q <= 4'b0000; else $Q \le \{Q[2:0], SI\};$ end endmodule SUNY - New Paltz Elect. & Comp. Eng.

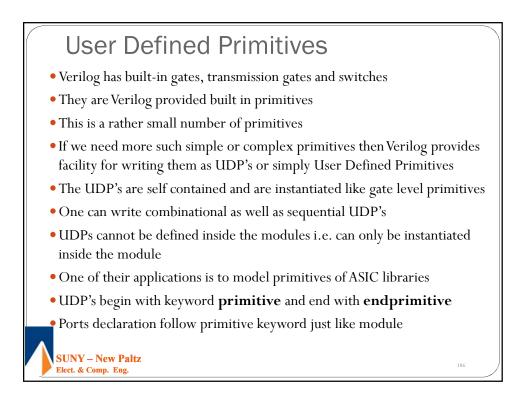

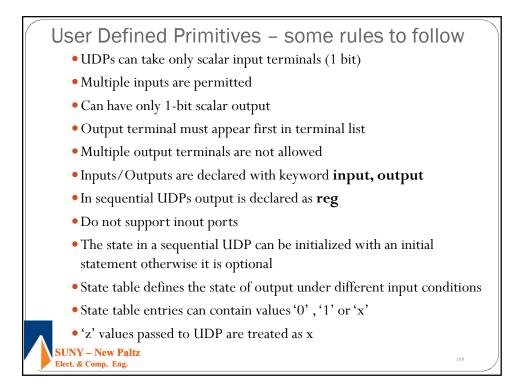

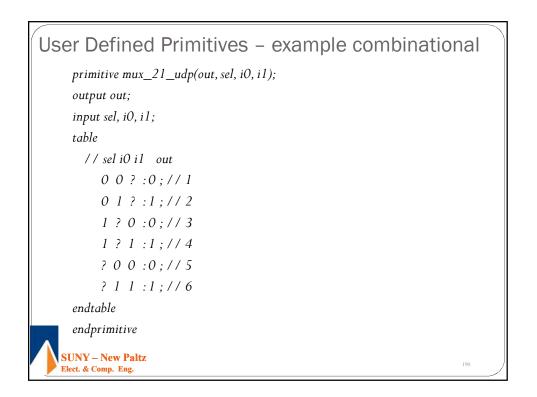

User Defined Primitives - when to use UDP's UDPs description is technology independent • UDPs cannot model timing parameters, hence functionalities that need to model timing parameters should be modeled as module • UDP is a lookup table, hence as the number of inputs increase table entries grows exponentially which in turn increases the memory requirement, therefore do not design UDP's with large number of inputs UDP state table should be specified as completely as possible because if certain combination of inputs is not specified, the default output for that combination will be 'x' primitive udp\_syntax (a, b, c, d); output a; *input b,c,d;* // UDP function code here endprimitive SUNY - New Paltz Elect. & Comp. Eng

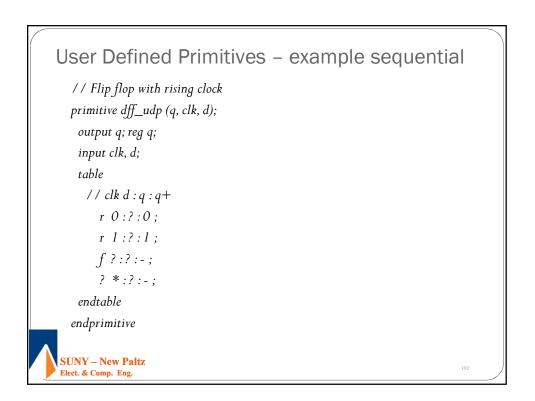

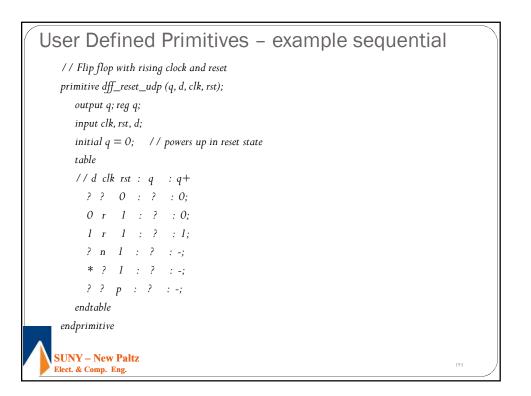

User Defined Primitives – example sequential

// Latch with active low clock

primitive latch\_udp(q, clock, data);

output q; reg q;

input clock, data;

table

// clock data q q+

0 1 :?:1;

0 0 :?:0;

1 ? :?:-;//-= no change

endtable

endprimitive